Percobaan 1 : J-K Flip Flop dan D Flip Flop

Kelebihan JK Flip-flop adalah tidak adanya kondisi terlarang atau yang berarti di beri berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluarannya / outputnya. berikut adalah symbol dan tabel kebenaran dari JK Flip-Flop.

D flip flop IC 7474 adalah Perangkat TTL. Ini memiliki input data dan jam; input ini disebut sinkron karena mereka beroperasi selangkah dengan pulsa clock, sedangkan preset dan reset adalah input asinkron. Mereka tidak tergantung pada pulsa clock.

3. Rangkaian [Kembali]

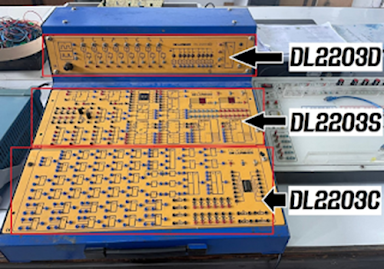

Gambar Rangkaian Percobaan

4. Prinsip Kerja [Kembali]

Prinsp kerja IC J-K flip flop modul d'lorenzo, yaitu ketika input S berfungsi aktif, maka input S akan mempengaruhi set nilai logika output Q (H7), lalu Q' (H6) diperoleh dari output Q (H7) yang diinverskan. Ketika R berfungsi aktif, maka input R akan mempengaruhi reset output Q (H7) kembali berlogika 0. Kondisi ketika salah satu inputan S atau R atau salah satunya aktif maupun keduanya non aktif pada inputannya, maka kondisi ini disebut kondisi input asinkron yang dimana input J, Clock dan K tidak akan aktif atau kita abaikan karena input S dan R yang akan mempengaruhi output Q (H7) dan Q' (H6). Namun jika input S dan R saling nonaktif, maka input J, clock, dan K akan memegang kendali dalam pengaruh hasil logika output Q (H7) dan Q' (H6).

Prinsp kerja IC D-flip flop yaitu dimana input J dan K disatukan, namun pada input K di NOT-kan pada modul d'lorenzo sehingga terbentuk IC D-flip flop. Prinsip kerjanya ketika input D berfungsi aktif ( aktif high berlogika 1 atau aktif low berlogika 0), maka input D akan mempengaruhi set nilai logika output Q (H4), lalu Q' (H3) diperoleh dari output Q (H4)yang diinverskan, input clock akan mempengaruhi input D terhadap output Q (H4) yang dimana jika clock aktif maka input D dapat mempengaruhi output Q (H4), namun jika nonaktif, maka input D tidak dapat mempengaruhi output Q (H4).

5. Video Percobaan[Kembali]

6. Analisis[Kembali]

Percobaan 1:

1. Bagaimana jika B0 dan B1 sama sama diberi logika 0, apa yang terjadi pada rangkaian?

Pada rangkaian JK flip-flop input set (S) dan reset (R) merupakan input dengan aktif low, maka saat B0 dan B1 diberi input berlogika 0, maka akan terbentuk input asinkron yang dimana input J, clock, dan K dapat diabaikan, maka input S dan R akan mempengaruhi kinerja output Q dan Q' yang dimana S dan R akan aktif low, sehingga output Q dan Q' akan berlogika 1

Karena output Q dan Q' sama-sama berlogika 0, maka kondisi ini dikatakan kondisi terlarang karena pada dasarnya rangkaian flip-flop merupakan rangkaian stabil pada dua kondisi (bistabil) dimana kondisi output rangkaian akan stabil pada keluaran kondisi yang berlawanan atau komplemen sesuai fungsi tetapan output.

Pada rangkaian, output kondisi saling berlawanan yaitu Q dan Q' dimana 2 kondisi output ini stabil, maka jika diperoleh output Q sesuai input set, maka output Q' akan invers terhadap Q, kedua kondisi output tersebut harus stabil sesuai fungsinya. Maka ketika S aktif low berlogika 0, nilai output Q menjadi aktif berlogika 1 dan ketika R aktif low berlogika 0, nilai output Q akan direset berlogika nol sehingga Q' berlogika 1.

Maka berdasarkan rangkaian diperoleh output sama-sama berlogika 1 yang dimana sesuai input sama-sama aktif low, maka kondisi ini dikatakan terlarang karena seharusnya salah satunya baik Q atau Q' berlogika nol dengan mengatur input S dan R saling komplemen, tidak boleh aktif bersama.

Oleh karena terjadi kondisi terlarang ini dengan kesamaan input aktif ini yang disebabkan input S dan R aktif bersama, maka output akan terganggu kestabilannya sehingga rangkaian akan tidak stabil sesuai kinerjanya.

2. Bagaimana jika B3 diputuskan/tidak dibubungkan pada rangkaian apa yang terjadi pada rangkaian?

Input B3 merupakan input dengan switch yang terhubung ke input clock pada IC JK flip-flop.

Jika aliran input B3 diputuskan terhadap clock maka proses kerja input saat kondisi sinkron akan terganggu karena saat kondisi input sinkron, input J dan K hanya akan terbaca oleh output ketika clock aktif (rise time atau fall time) oleh input, sehingga ketika B3 diputuskan lalu secara bersamaan kondisi input dalam kondisi sinkron dan clock tidak aktif karena B3 diputus, maka yang akan terjadi rangkaian akan tetap aktif namun input J dan K tidak akan terbaca oleh output walaupun input J dan K telah divariasikan.

3. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada Flip-Flop!

- Kondisi Toogle merupakan kondisi flip-flop dimana saat 1 atau 2 input (kondisi input asinkron pada S dan R atau sinkron pada J dan K) dalam keadaan aktif, maka output yang dihasilkan antara dua output yang saling komplemen (Q dan Q') akan diperoleh keluaran logika ganda yang saling berkomplemen dari output sebelumnya dan saling bergantian, yaitu saat output Q berlogika 1 maka Q' berlogika 0 atau saat Q berlogika nol maka Q' berlogika 1 yang dimana sesuai pengaturan clock pada pergantian input high atau low pada clock sebagai pemicu pergantian output.

- Kondisi not change adalah kondisi flip-flop ketika 1 atau 2 input (kondisi input asinkron pada s dan r atau sinkron pada J dan K) low, maka diperoleh output tetap (tidak berubah) sesuai output yang diset sebelumnya, yaitu ketika output sebelumnya Q = 1 dan Q' = 0, maka ketika di set input low tidak mengalami perubahan pada output dan output akan tetap Q = 1 dan Q' = 0, begitupun seterusnya jika diuji dengan output sebelumnya yang lain dengan input sama-sama low, tidak akan berubah (tetap).

- Kondisi terlarang adalah kondisi yang tidak boleh digunakan karena kedua output flip-flop yang saling berkomplemen berlogika 1 secara bersamaan pada kondisi flip-flop saat input S dan R (kondisi asinkron) diset aktif (aktif high atau low) bersamaan. Dikatakan kondisi terlarang karena pada dasarnya rangkaian flip-flop merupakan rangkaian stabil pada dua kondisi (bistabil) di mana kondisi output rangkaian akan stabil pada keluaran kondisi yang berlawanan (komplemen) sesuai fungsi tetapan output. Seharusnya salah satu output baik Q atau Q' harus berlogika nol dengan mengatur input S dan R saling komplemen atau sama-sama low (nonaktif), tidak boleh aktif bersama. Oleh karena terjadi kesamaan input aktif yang disebabkan S dan R aktif (high atau low) bersamaan, maka output akan terganggu kestabilannya, sehingga flip-flop kinerjanya tidak stabil, kondisi ini dikatakan kondisi terlarang.

7. Download[Kembali]

.png)